コンピュータチップ内では、半導体の微細化によって素子が原子のサイズに近づいており、性能を上げるためには、回路、ならびにアーキテクチャ・レベルの技術が不可欠です。そこで、二相ラッチとタイミング故障検出を組み合わせた方式を提案しています。

研究背景・目的

世の中では、ムーアの法則の終焉が叫ばれていますが、その科学的な根拠であるデナードスケーリング(比例縮小則)は、20年近く前にすでに終焉を迎えています。微細化に応じて電源電圧を下げることができなくなり、消費電力と発熱がチップの性能を制限する主要因となっています。その原因の一つとして、チップ内の素子の性能のランダムなばらつきが挙げられます。これは、半導体の微細化によって素子のサイズが原子のサイズに近づいてきたためで、半導体技術によって解決することは困難です。そこで、回路、ならびにアーキテクチャ・レベルの技術が不可欠となります。私たちは、二相ラッチとタイミング故障検出・回復を組み合わせたクロッキング方式の研究を進めています。

研究内容

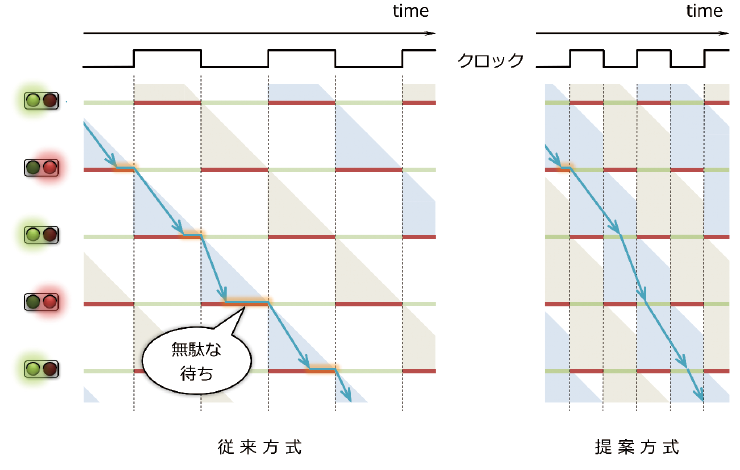

提案は、端的に言えば、二相ラッチとタイミング故障検出を組み合わせたものです。この組み合わせによって、ラッチが開いている時に信号が通過できるようになります。回路中を進むデジタル信号を道路を走る車に喩えると、図のように、目の前の(交通)信号が次々青に変わっていき、赤信号につかまらずに走り続けられる状態と言えます。このとき回路は長大な組み合わせ回路のように動作し、素子のランダムなばらつきは大数の法則によって0に近づきます。動作周波数の上限は、タイミング故障の検出限界で決まり、通常の方式のちょうど2倍となります。このバジェットを電源電圧の低下に振り向けることもできます。

産業応用の可能性

提案のクロッキング自体は、基本的にはクロックを用いるすべてのLSI(Large-scale Integrated Circuit:大規模集積回路)に応用可能です。ただし、タイミング故障から回復するため、プロセッサが例外を起こした命令を再実行するように、何らかのエラーに対して再実行する機能が必要です。

私たちは、フリップ・フロップ(FF)を用いた通常の設計に対して自動的に変換を行うツールを開発しています。現在、RISC-Vアーキテクチャのスカラ・プロセッサRocketに対して、提案の方式を適用し、FPGA(製造後に購入者や設計者が構成を設定できる集積回路)上に実装、動作させることで検証を進めています。今後は、スーパスカラ・プロセッサ「雷上動」に適用し、LSI上に実装する予定です。

図)回路中を進むデジタル信号を道路を走る車に喩える。従来方式(左)ではすべての信号につかまる。一方、提案方式(右)では信号が青のうちに通過できる。

研究者の発明

❖特許第5589169号:半導体集積回路

❖特許第5181127号:半導体集積回路