平成 25 年 10 月 8 日 大学共同利用機関法人 情報・システム研究機構 国立情報学研究所 日本電信電話株式会社

# 報道関係者 各位

# 世界初、量子コンピュータを理論的に統合評価する方法を確立 ~ソフトウェア的アプローチがパフォーマンス向上の決め手!~

情報・システム研究機構 国立情報学研究所(所長 喜連川 優、以下 NII)の根本香絵教授とその研究チームは、日本電信電話株式会社(代表取締役社長 鵜浦 博夫、以下 NTT)物性科学基礎研究所と共同で、世界初となる量子コンピュータを理論的に統合評価する方法を開発しました。最近、量子コンピュータの基礎となる技術が、世界的に目覚ましい実験的成果を挙げています。そこでわれわれは、現時点で最も有望な大規模量子コンピュータの方法である「誤り耐性(フォールトトレラント)量子コンピュータ\*\*1」について、上層のアルゴリズムから下層の素子制御までのすべての技術レイヤを漏れなく統合するという、実際の動作の流れに従って理論的にアルゴリズムを解析し、量子コンピュータの性能を評価する方法を世界で初めて確立しました。

またこの方法を用いて、実際にショアの素因数分解アルゴリズム\*\*2 を解析し、量子コンピュータのベンチマークの指針を示すことにより、量子コンピュータのパフォーマンスは、素子の完成度よりも、ソフトウェア的アプローチ(基本素子の配列、使い方、組み合わせ等)によって大きく変わることを明らかにしました。

■本研究の詳細は、英国科学誌 Nature Communications 2013 年 10 月 3 日号に掲載されました。

Nature Communications: <a href="http://www.nature.com/naturecommunications">http://www.nature.com/naturecommunications</a>

論文タイトル: Requirements for fault-tolerant factoring on an atom-optics quantum Computer

3 October (2013) DOI:10.1038/ncomms3524

# 【背景】

従来の技術では手に負えない問題へアプローチする量子コンピュータや、安全な通信を目指した量子暗号などの量子情報科学技術の研究が、世界中で活発化しています。中でも解くのに時間のかかる大きな問題や長距離通信のように拡張性(スケーラビリティ)が必須のシステムでは、誤りに対する耐性を持たせることで、大規模化を保証できることが理論的に知られています。

また、量子コンピュータの基本素子である量子情報素子の研究も進んでおり、近年の実験的成果では、世界的に見て 10 量子ビット程度まで実現されるようになってきたものの、誤り耐性を持つ量子技術は、多くの量子ビットを必要とすることがわかっています。ではこのような基本的な素子技術を結集して、大規模量子コンピュータが作られたなら、それはどのくらいの性能で、どのくらいのリソースを必要とするでしょうか?

この問いに答えるためには、まず量子コンピュータの組み立て方を明らかにする必要があります。 我々はまず 2009 年に、量子コンピュータのアーキテクチャを示しました。また、量子コンピュータの 動作を時間を追って記述し、性能を評価するためには、情報処理の一連の流れ(ソフトウエア)まで含めて考慮する必要があります。しかし従来のコンピュータとは異なり、アルゴリズムから素子までのすべての技術レイヤを統合する困難さから、これまで量子コンピュータ全体としての評価は不完全でした。

# 【研究成果】

今回、我々は、NIIが蓄積してきた量子コンピュータのアーキテクチャに関する知見とNTTが有する量子素子に関する知見を生かして、大規模な誤り耐性量子コンピュータにおける構成素子からアルゴリズムまでの技術レイヤを統合し、量子コンピュータの性能評価手法を世界で初めて確立しました。

性能評価の結果から、量子コンピュータの性能は、素子の完成度よりも、基本素子の配列、使い方、組み合わせといったソフトウエア的アプローチに依存することが判明しました。

本手法により、量子コンピュータの統一的な設計指針の策定が可能になり、大規模な量子コンピュータの実現に向けてとるべき指針が明らかになりました。

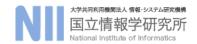

#### 各技術レイヤとその統合について(NII、NTT):

最下層の構成素子から最上層のアルゴリズムまで、新たに導入すべきレイヤをも含めて特定し、 大規模な誤り耐性量子コンピュータに不可欠なすべてのステップを明らかにしました。

技術レイヤの特定と統合は、構成素子に光モジュールを採用して行いました。構成素子である「光モジュール」は、「光と量子ビット(原子や固体中の2準位系)」から成り、光と量子ビットの合成系を制御することで、エンタングルメント(量子もつれ)を生成する素子です。この素子を3次元に規則的に配置し、「光モジュールネットワーク」を構成します。この素子のネットワークに、「光モジュール上のスケジュール」で決められた通りに光子を送り込むことで、3次元の格子状にエンタングルした光子列が生成されます。この光子列は3次元トポロジカル量子計算\*3のリソースで、一定の規則に従って光子を測定することで、「誤り訂正符号により保護された量子ビット」(ロジカル量子ビット)上で量子計算を進めることができるようになります。

「光モジュールネットワーク」上に割り当てられたロジカル量子ビットは誤り訂正が可能ですが、量子計算全体に誤り耐性を持たせるためには、誤り耐性のあるゲートの実装が必要です。誤り耐性ゲートの実行ができるよう、量子コンピュータの「リソース・アロケーション」を決めてハードウエアのリソースを配分します。誤り耐性のあるゲートの種類はごく限られているため、アルゴリズムからユニバーサル・ゲートセット<sup>※4</sup> への分解により得られる「量子回路」をさらに、誤り耐性のあるゲートセットへ分解して、「誤り耐性のある量子回路」を得ます。ここでさらに、ハードウエアのもつ制限を考慮してゲートの「スケジューリング」を行うことで、実行可能なゲート列が生成されます。

各技術レイヤのリストは、他のスケーラブルな量子コンピュータの実装方式へも適用でき、実行可能性のチェックリストとして機能する他、リソースやパフォーマンスのベンチマークへ用いることができます。

# 量子物理から量子コンピュータ・アーキテクチャーまで 量子物理制御:光と量子ビット(原子や固体中の2準位系)

図 1:技術レイヤ統合の概念図「量子物理から量子コンピュータ・アーキテクチャまで」

# ・リソース・パフォーマンス評価について(NII):

「研究の背景」に記したように、素子の技術や量子誤り訂正符号の理論はこれまでそれぞれ独立したテーマとして研究されてきました。このたびそれらの技術が、統合的な視点から全体を形作

るための各レイヤとして特定されたことにより、実装しようとするアルゴリズムが、各素子に対してどのような振る舞いを具体的に要求しているのか書き下すことが可能となりました。これにより、量子コンピュータのリソースと性能を評価できるようになりました。

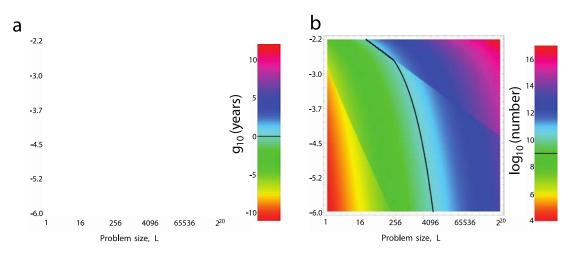

ショアの因数分解について量子コンピュータのパフォーマンスとリソースについて数値的に解析しました。図 2(a)は横軸に問題の大きさ(因数分解する数の大きさ)、縦軸にモジュールの誤り率を表しており、これに計算時間を色でプロットしたものです。黒線は 1 年のラインを示しており、ここから計算時間はモジュールの誤り率にあまり依存しないことがわかります。一方、図 2(b)は、モジュールの数を色でプロットしたもので、黒線は 10 億モジュールのラインを示しています。

図 2:(a) 横軸に問題の大きさ(因数分解する数の大きさ)、縦軸にモジュールの誤り率

(b) モジュールの数を色でプロットしたもので、黒線は 10 億モジュールのライン

# 【本研究成果の意義】

量子コンピュータのパフォーマンスは、素子の完成度の追及よりも、オペレ―ションをも含めたソフトウエアの工夫による高速化の方が有効であることが世界で初めてわかり、大規模な量子コンピュータを実現する上でのソフトウエアの重要性が示されました。これは、ソフトウエアを改善すれば、実現すべき素子の技術レベルの低減化も可能であることを示唆するものです。素子開発を行う実験チームへの新たな指針としても、大いに役立つものと言えます。

## 【今後の予定】

ソフトウエアを改善すれば、量子コンピュータのパフォーマンスが大きく向上する可能性があることが、明らかになりました。今後は、量子コンピュータの実現に大きく貢献できることが期待される「ソフトウエア」という切り口からも、研究を進めていく予定です。

そのため、NII では、先にリリースしたトポロジカル量子回路の最適化問題をゲーム化した『meQuanics』を用い、オープン・サイエンス的手法も取り入れて、研究を進めていきます。また素子開発チームと連携し、随時フィードバックを行っていく予定です。

また NTT では、光と電子を強く相互作用させる光モジュールの実現に向けた研究にも取り組む 予定です。

# 用語解説

※1 誤り耐性量子コンピュータ

素子は必ず誤りを起こすため、情報を誤り訂正符号で守ることが一般に行われる。量子情報処理 の場合には、量子誤り訂正符号を用いて誤りから守られた量子ビット(ロジカル量子ビット)を用い る。ひとつの誤りが伝搬しないように工夫することで、大規模化を可能にする方法が誤り耐性であ る。

※2 ショアの素因数分解アルゴリズム

量子回路への分解など、もっとも詳細に研究されている量子アルゴリズム。

※3 3次元トポロジカル量子計算

量子誤り符号と量子計算が一体化された量子計算モデル。格子状のエンタングルした量子ビット上で、3次元のトポロジカル構造を操作することで、量子計算を行うことができる。

※4 ユニバーサル・ゲートセット

任意の量子情報処理を行うために必須となるゲートセット。古典コンピュータのコンプリート・ゲートセットの量子的拡張である。

【本件に関するお問い合わせ】

国立情報学研究所 教授 根本 香絵

TEL: 03-4212-2561

E-mail: nemoto@nii.ac.jp

【報道に関する問合せ】

国立情報学研究所 広報チーム(坂内)

Tel:03-4212-2164 E-mail:bannai@nii.ac.jp

NTT先端技術総合研究所 広報担当

Tel: 046-240-5157 E-mail: a-info.ntt.co.jp

# 【謝辞】

本研究は、FIRST プログラム、新学術領域「量子サイバネティクス」での成果を含みます。