# ULP-HPCのためのインターコネクト技術

**Interconnect Technology for ULP-HPC**

# 鯉渕 道紘 藤原 一毅

Michihiro KOIBUCHI Ikki FUJIWARA

# 何がわかる?

最新のスーパーコンピュータは数十万個のプロセッサコアを並列に動かすことで1秒間に10の15乗回以上の演算を実行しています.しかし,システム性能はコア間の通信遅延と消費電力により律速されつつあるため,さらなる劇的な性能向上が難しい状況です.この限界をどう突破するか?

## どんな研究?

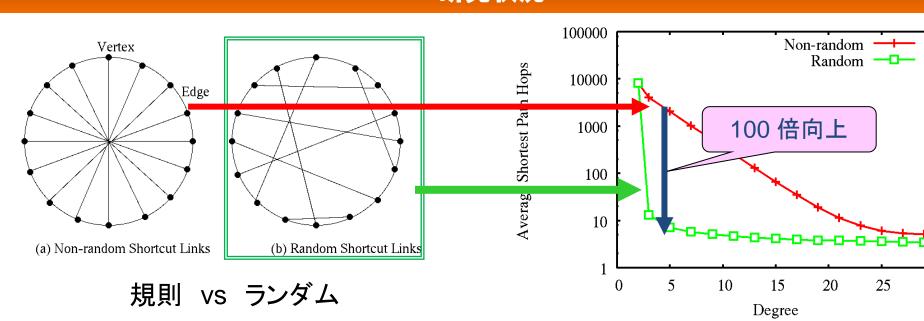

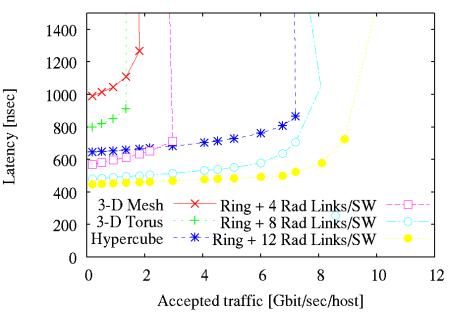

スパコンのインターコネクトは、これまでトーラス、Fat ツリーなどの強い規則性を持つトポロジが採用されて きました。しかし、これらのトポロジでは次世代スパコンのシステム要求である通信遅延1 $\mu$ 秒を達成することが難しい。我々は、この限界を、「ランダムにリンクを接続したトポロジ」で突破できることを示します。

# 状況設定

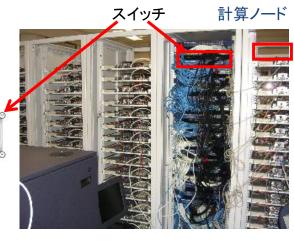

スパコンのインターコネクトの現状

- スイッチ遅延が 100ナノ秒以上

- 多くの通信のメッセージサイズ が3KB未満

- 要求されているシステム最長 遅延が1 µ 秒

本成果は東工大,東大,電通大との 共同研究であるJST CREST ULP-HPC(電力性能比1,000倍向上)の ひとつの要素技術

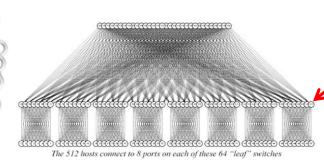

トーラス@京コンピュータ

Myrinet Clos (Myricom社)

30

## 研究状況

### スパコンのトポロジとしてランダムショートカットトポロジを探求した結果、

- 遅延35%削減,スループット向上

- 既存のトポロジとほぼ同配線コスト

- 配線の柔軟性による高耐故障性のメリット有

- 高いスケーラビリティ

- ランダム性による性能差のばらつきは微小

次世代スパコンのインターコネクトを支えることが可能

#### 発表論文

[1] M.Koibuchi, H. Matsutani, H.Amano, D. Frank Hsu, H. Casanova, A Case for Random Shortcut Topologies for HPC Interconnects, The ACM IEEE International Symposium on *Computer* Architecture(ISCA), June 2012, to appear [2] J. Flich, T. Skeie, A.Mejia, O. Lysne, P. Lopez, A. Robles, J. Duato, M. Koibuchi, T. Rokicki, and J. C. Sancho, ``A Survey and Evaluation of Topology Agnostic Routing Algorithms", IEEE Transactions on Parallel and Distributed Systems, Vol.23, No.3, pp.405-425, Mar. 2012

■■ 連絡先:鯉渕 道紘/国立情報学研究所 アーキテクチャ科学研究系 准教授 ■■ TEL:03-4212-2575 FAX:03-4212-2120 Email:koibuchi@nii.ac.jp

NII