研究背景・目的

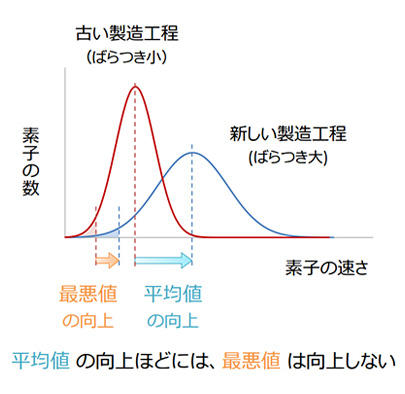

LSIが微細化されるにつれて、回路素子の性能の「ばらつき」が問題になりつつあります。

本研究では、「今日できなかった分は明日やる」ことで「ばらつき」に対処するディジタル回路の構成方式を研究しています。「ばらつき」の問題を乗り越えて、ディジタル回路(コンピュータ)の処理速度の向上・消費電力の削減を目的としています。

研究内容

LSIの微細化が進むと、性能が向上する一方で、製造誤差も相対的に増大しています。現在、LSIの最小加工寸法は原子数十個分程度となっており、原子一個分の誤差でも性能が大きく変わってしまいます。

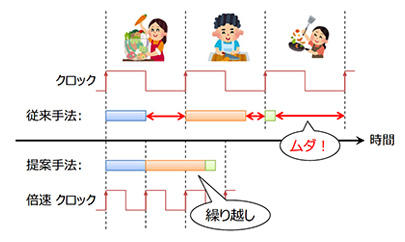

従来の「ワーストケース設計」では、すべての素子の性能が最悪の場合でも間に合うようにクロック速度を設定しており、「ばらつき」が大きいとムダが大きくなってしまいます。

私は、ダイナミック・タイム・ボローイングを可能とするクロッキング方式を提案しています。これは、二相ラッチ方式と、動的タイミング故障検出の組み合わせです。

この方式では、あるステージの実効的な遅延が大きかった場合、超過時間を次のステージへと繰り越すことができます。

それでも間に合わない場合には、タイミング故障として検出し、回復を行います。

このことによって、ワーストケース遅延ではなく、実際の遅延で、回路は動作することができます。

産業応用の可能性

- 基本的には、すべてのLSIに応用することができます。

連絡先

五島 正裕[アーキテクチャ科学研究系 教授]

goshima[at]nii.ac.jp ※[at]を@に変換してください

関連リンク

Recommend

さらにみる